Designers face many unique challenges when developing systems used in space that do not exist for terrestrial systems.

Among these are the need to ensure the trustworthiness of intellectual property (IP), overcome a lack of widespread industry support for radiation-tolerant devices, and amortize high design costs across low production volumes.

These challenges are particularly important when evaluating processors for space designs, and difficult to solve using a closed processor architecture. That is why designers are increasingly choosing the RISC-V fixed instruction set architecture (ISA), in a major industry shift aimed at solving unique space system challenges while realizing other multiple and valuable benefits.

Understanding RISC-V

Processor options for space designs are limited to closed architectures such as ARM, RAD (Power PC), Leon, and SPARC varieties. Although it is unlikely these processors will lose popularity in the foreseeable future, the open RISC-V processor ecosystem is poised for rapid growth in the space community.

Because the RISC-V ISA is open, the design of the processor micro-architecture is flexible. Vendors are free to implement whichever architecture they deem best for their application. This allows broad innovation for designs that, for instance, have some operations accelerated in hardware, or perhaps require a processor designed for the lowest possible power consumption.

To enable broad use, the non-profit and member-controlled RISC-V Foundation opened the instruction set and also froze the base instruction set in 2014. This allowed the market to dictate what type of processor micro-architectures to develop. Thus, all the variations in a RISC-V micro-architecture are acceptable because the underlying ISA is open and fixed. Designers can now fully optimize a processor architecture for their specific requirements.

RISC-V for Space Applications

Space system developers can benefit from RISC-V whether their design uses a real-time OS (RTOS) or is a “bare metal” implementation for a virtualized environment.

RISC-V code written today will be compatible with RISC-V processors developed years in the future, enabling designers to seamlessly migrate from one RISC-V core to another. Most other processors typically add instructions with each new generation, which forces the designer to recompile and update software. However, because the RISC-V instruction set is frozen and eliminates this requirement, the space market can rapidly adopt RISC-V as a new standard open architecture for direct native hardware implementations. That is one of the main reasons RISC-V is attractive for the space market; however, there are additional factors that make RISC-V a better choice than other processor architectures.

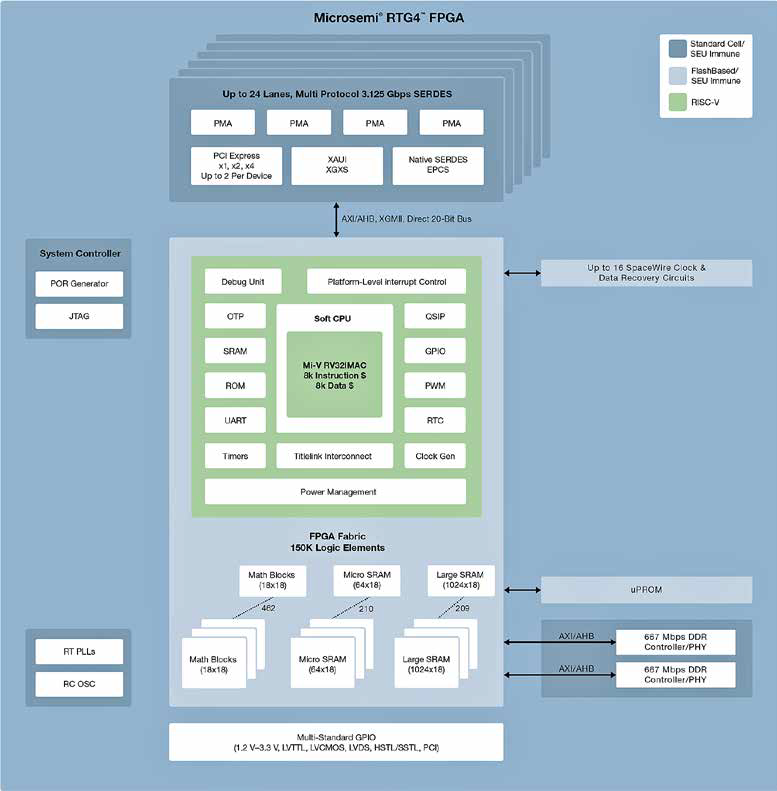

First, RISC-V-based designs add trust to IP by giving designers the option to view the register transfer level (RTL) code — something that cannot be done with closed processor architectures. One example of this capability is Microsemi’s family of RISC-V IP cores for the company’s RTG4 radiation-tolerant FPGAs (see Figure 1). These 32-bit RISC-V IP cores and the source RTL code are available for users.

With the ability to inspect the RTL, designers can ensure that the IP contains only intended functions and does not contain RTL code with malicious intent.

In this way, program supply chain risk assurance management objectives can be met. The initial RISC-V IP for RTG4 runs at 70 MHz and consumes only 8 percent of the logic resources provided in the RTG4 FPGA. RISC-V is not limited to 32-bit implementations; a 16-bit compressed instruction set as well as a 64-bit and 128-bit ISA are also available and ratified.

A second additional benefit of the open ISA is that RISC-V creates a “royalty-free” processor sub-system. As the RTL code is available in RISC-V IP cores, designers have the flexibility to modify and implement designs in any hardware, for multiple applications

or environments.

For example, designs that operate in deep space generally require the latest radiation-tolerant FPGA architectures to protect them against harmful single event and total dose effects. In contrast, designs used in the less demanding environments of sub-orbital space and certain Low Earth Orbit (LEO) craft can sometimes use a different FPGA with designer-instantiated triple-redundancy mitigation techniques where needed and don’t have the same stringent quality conformance inspection and QML manufacturing flows.

Clearly, the development of different designs for each market is preferable, using different FPGAs. It is much easier to do this with royalty-free RISC-V cores, which only require a free Berkeley Software Distribution (BSD) software license that imposes minimal restrictions on IP use and redistribution.

Longevity is the third major benefit of RISC-V, which enables designers to rely on the fixed ISA and preserve software investments across multiple implementations. Because the RISC-V ISA is fixed, space designs that are often expected to be reused over periods of several years, or even decades, can depend on software continuity. Once the software code is written and validated, it can be run on any RISC-V core forever.

The initial manufacturing can be completed with a soft RISC-V core in one FPGA and the code will be completely compatible with a future FPGA implementation, or even an ASIC. As the design of modern systems tends to rely increasingly on software, the ability to reuse previously validated and deployed software code from one generation of a system design to another can result in significant cost and schedule savings.

Leveraging a RISC-V Ecosystem

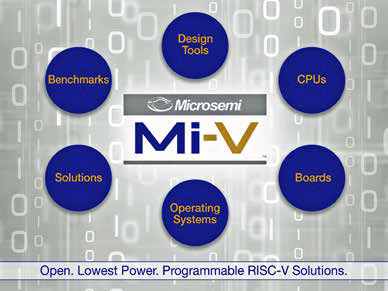

The value of RISC-V can be enhanced through an ecosystem of devices, cores and development tools. One example is Microsemi’s recently announced Mi-V RISC-V ecosystem, which contains the first FPGA-based open architecture RISC-V IP core and a comprehensive software integrated development environment (IDE) solution called SoftConsole (see Figure 2).

A RISC-V ecosystem makes it easier for space designers to deploy a RISC-V IP core in multiple flash-based FPGAs. Designs requiring high security, for instance, might require an FPGA that enables storage of the boot code for soft core in secure NVM, preventing malware or a root kit from being installed in the system. Embedded engineers can leverage the benefits of the ecosystem’s RISC-V IP in their custom FPGA designs by using design suites that incorporate numerous third-party tools. The Mi-V ecosystem’s Soft Console IDE, for example, includes the ThreadX RTOS that Express Logic has ported to RISC-V, and an instruction set simulator for the Mi-V RISC-V IP core that Imperas has recently introduced.

Another important ecosystem feature is a set of reference designs for evaluating a RISC-V core and writing software executable code. For software code development, the IDE should ideally be hosted on a Linux or Windows platform and provide complete development support, including a C or C++ compiler and complete debugger capability.

With the mainstream adoption of RISC-V, space designers now have an alternative processor architecture to consider. The advantages of trusted IP, open RTL, and lower costs can benefit virtually every space application. Customers can also count on the fixed ISA to ensure software compatibility and longevity of the architecture.

The RISC-V processor is also compelling for applications where inspection and stringent certification is important. These and other benefits of RISC-V cores are enabling a new generation of innovation for space designers.

For background information about RISC-V and its member organizations, visit www.riscv.org.

If you are ready to initiate a design and start RISC-V core coding, head over to Microsemi’s Github site, github.com/RISCV-on-Microsemi-FPGA.

The authors

Left: Ted Marena is the Director of Marketing, FPGA/SoC Marketing, at Microsemi Corporation.

Right: Ken O’Neill is the Director of Marketing, Space and Aviation, at Microsemi Corporation